Arithmetic Logic Unit (ALU)

The ALU is the core combinational block in a CPU datapath. In this manual, you will build an ALU supporting four operations:

- Two’s-complement add:

- Two’s-complement subtract:

- Bitwise AND:

- Bitwise OR:

Design idea:

- Reuse one adder for both add and subtract.

- Compute arithmetic (add/sub) and logic (and/or) results in parallel.

- Use a multiplexer to select the final output based on an opcode.

Experiment: Adder/Subtractor

Section titled “Experiment: Adder/Subtractor”Objectives

Section titled “Objectives”- Understand the two’s-complement identity: .

- Learn how to reuse an adder to implement subtraction.

Principles

Section titled “Principles”In two’s-complement, negation is . Therefore:

So if we conditionally invert B and conditionally add 1, we can implement subtraction with the same adder used for addition.

Environment

Section titled “Environment”- Simulator: Logisim Evolution

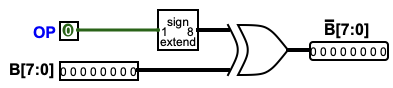

Task 1: Controlled inverter (for B)

Section titled “Task 1: Controlled inverter (for B)”Use XOR’s properties:

Let OP=0 mean add, OP=1 mean subtract.

- Place input pin OP.

- Place an 8-bit input pin B[7:0] and an 8-bit output pin (call it ~B[7:0] initially).

- Place an 8-bit XOR gate.

- Use a bit extender to expand OP (1 bit) to 8 bits, then XOR it with B[7:0].

Figure 2.12: Controlled inverter using XOR (OP selects pass-through vs bitwise inversion of B).

Verify behavior for OP=0 (no inversion) and OP=1 (inversion).

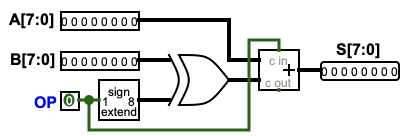

Task 2: Adder/subtractor

Section titled “Task 2: Adder/subtractor”- Add an 8-bit input A[7:0].

- Rename the previous ~B output to S[7:0] (the final result) and disconnect it from the XOR output.

- Place an 8-bit adder component.

- Wire:

- adder operand 1 ← A[7:0]

- adder operand 2 ← (B[7:0] XOR OP)

- adder ← OP

Figure 2.13: Adder/subtractor circuit (reuse one adder for add and subtract via OP).

Test examples:

- Addition (OP=0):

- A=00000101 (5), B=00000011 (3) → S=00001000 (8)

- A=11111100 (-4), B=00000011 (3) → S=11111111 (-1)

- Subtraction (OP=1):

- A=00001001 (9), B=00000101 (5) → S=00000100 (4)

- A=00000101 (5), B=00001001 (9) → S=11111100 (-4)

Also compare your results with the unified equation:

Results

Section titled “Results”- Circuit screenshots

- Test records: at least 6 cases total

- ≥3 addition cases (include at least one case involving negative numbers)

- ≥3 subtraction cases (include at least one case where A < B)

- For each case, record OP, A, B, S in both binary and signed decimal (two’s complement).

Questions

Section titled “Questions”- Give a unified expression for S (hint: consider the XOR and together). Explain why it becomes when OP=0 and when OP=1.

- Why should the bit extender use sign extension?

- Can the adder carry-out be used as an overflow indicator?

- For unsigned addition, is a correct overflow signal? Why?

- For signed two’s-complement add/sub, is still reliable? If not, how do you detect signed overflow?

Extension

Section titled “Extension”Design and add a signed overflow signal. Provide at least two test cases that overflow (e.g., positive overflow and negative overflow), and explain why the signal should assert.

Experiment: Arithmetic Logic Unit (ALU)

Section titled “Experiment: Arithmetic Logic Unit (ALU)”Build an ALU that supports the four operations above. The key structure is:

- compute all candidate results in parallel

- select one result using a MUX controlled by ALUCtrl

Inputs and outputs

Section titled “Inputs and outputs”- Inputs: A[7:0], B[7:0] (interpreted as signed two’s-complement)

- Control: ALUCtrl[1:0]

- Output: Y[7:0]

- Flag: Z (1 if Y == 0)

Design hints

Section titled “Design hints”- Many gates (including MUXes) can be configured to operate on multi-bit buses in Logisim Evolution.

- Arithmetic and bitwise logic can be computed in parallel.

- Use a MUX to select the final Y.

Results

Section titled “Results”-

ALU circuit screenshots:

- show A[7:0], B[7:0], ALUCtrl[1:0], Y[7:0]

- clearly show the four parallel result paths and the final MUX selection

- show how you generate Z (how you detect Y == 0)

-

Functional test record (table form):

- ≥8 test cases covering all four operations (≥2 cases per operation)

- for each case record: ALUCtrl, A, B, Y (binary), Y (signed decimal), Z

- include ≥2 cases where Y == 0 to validate Z

Example record table:

| ALUCtrl | A (bin) | B (bin) | Y (bin) | Y (dec) | Z |

|---|---|---|---|---|---|

| … | … | … | … | … | … |

Questions

Section titled “Questions”- Why do ALUs often use “parallel computation + MUX selection”? Discuss hardware reuse, combinational delay, and/or structural clarity.

- Is the encoding of ALUCtrl unique? Why/why not?

Extension

Section titled “Extension”- Add a negative flag N (for two’s complement, it’s the MSB: Y[7]).

- Add a signed overflow flag V (consider add vs subtract separately).

- Add a carry/borrow flag C.

- Extend the ALU with an additional operation (XOR, compare, etc.), expanding ALUCtrl width and MUX inputs.