Mapping Strategies (Basics)

To describe a cache, common parameters include:

- Capacity (bytes)

- Block size (bytes per block)

- Number of blocks

- Number of sets

- Associativity (ways)

A cache is organized as: sets → ways → lines (each line holds one block plus metadata such as valid/dirty/tag).

Different structures are essentially different choices of and :

- Direct-mapped:

- -way set-associative:

- Fully associative:

Direct-mapped

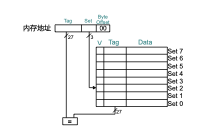

Section titled “Direct-mapped”In direct-mapped caches, each set has exactly one line.

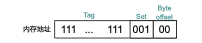

Figure 8.1: Example address partitioning for a direct-mapped cache.

Figure 8.2: Example direct-mapped cache structure (V = valid).

Set-associative

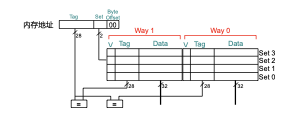

Section titled “Set-associative”In an -way set-associative cache, a memory block maps to one set, but may occupy any way within that set. Tags for all ways in the set are compared in parallel.

Figure 8.3: Example 2-way set-associative cache structure.

Fully associative

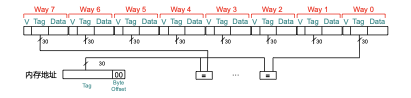

Section titled “Fully associative”Fully associative is the extreme: and . Any block may be placed in any line; there is no set index field.

Figure 8.4: Example fully associative cache structure.